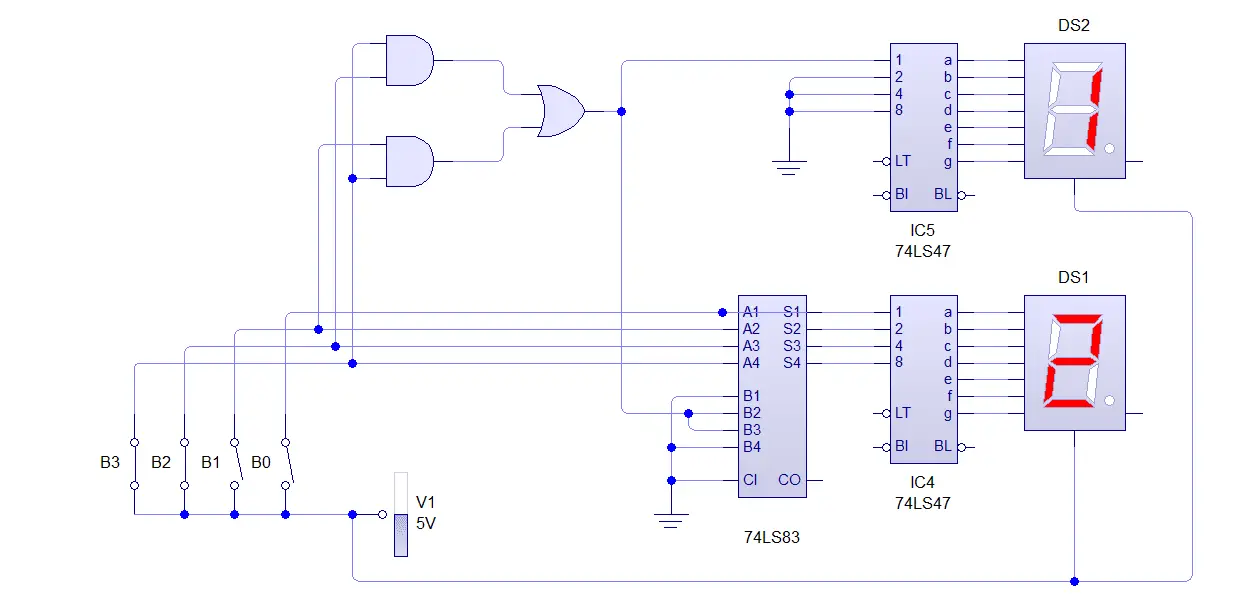

Sumador de 4 bits proteus

sumador binario de 4 bits logisim

Sumador-Substanciador binario de 4 bitsEn los circuitos digitales, un Sumador-Substanciador binario es aquel que es capaz tanto de sumar como de restar números binarios en un solo circuito. La operación que se realiza depende del valor binario que tenga la señal de control. Es uno de los componentes de la ALU (Unidad Lógica Aritmética). Este circuito requiere conocimientos previos de Puerta Exor, Suma y Resta Binaria, Sumador Completo. ¡Atención lector! No dejes de aprender ahora. Practicar el examen GATE bien antes del examen real con la materia y cuestionarios generales disponibles en GATE Test Series Course.Learn todos los conceptos GATE CS con clases en vivo gratis en nuestro canal youtube.Lets considerar dos números binarios de 4 bits A y B como entradas al circuito digital para la operación con dígitos A0 A1 A2 A3 para A

adderelectronics

¡Hola alumnos! Espero que estéis teniendo un día productivo. Bienvenidos de parte del equipo de Los Proyectos de Ingeniería. Estamos comenzando un nuevo tutorial que es una pieza completa de información sobre un Circuito lógico. El circuito que estamos aprendiendo hoy es el Sumador Completo. En nuestro anterior tutorial, hemos visto el Sumador Completo de 2-Bits usando Puertas Lógicas en el software Proteus, hoy vamos a diseñar y simular el Sumador Completo de 4-Bits usando Puertas Lógicas en Proteus. Vamos a discutir los siguientes temas en la conferencia de hoy:

SumadoresEn el sistema informático, la computación es un procedimiento importante. Los sumadores juegan un papel vital en este proceso. En primer lugar, vamos a definir los sumadores: «Los sumadores son los circuitos lógicos que están especialmente diseñados para sumar dos o más números en un sistema» En el mundo de la electrónica, los sumadores se utilizan para sumar los bits. El sistema informático depende del flujo de bits y del cálculo de los mismos. Los sumadores toman la entrada en forma de bits y realizan la suma según el tipo de sumador utilizado:

sumador-substanciador de 4 bits

TAMS / Java / Hades / applets: contents | previous | nextHadesAppletscontentsvisual index introduction std_logic_1164 gatelevel circuits delay models flipflops adders and arithm… half-adder a… ripple-carry… Sumador BCD con selección de… Sumador CLA (8… Sumador CLA (1… Generador CLA Bloque sumador CLA, sumador lento/sub… 7485 comparador 7485 comparador 74181 ALU de… 74181 ALU de… 74181+74182 … 74182 CLA ge… Hamming-weight Hamming-weig… integer mult… square calcu… square root … carry-save a… Contadores basados en CSA LFSR y memorias de autocomprobación Lógica programable Editor de máquinas de estado Demostraciones varias E/S y pantallas Relés de reloj DCF-77 (conmut… Circuitos CMOS (conmutadores… Lógica RTLIB Registros RTLIB Procesador Prima D*CORE MicroJava Cosimulación Pic16 Cosimulación Mips R3000… Procesamiento de imágenes Intel MCS4 (i4004) … [Sch04] Codeumsetzer [Sch04] Addierer [Sch04] Flipflops [Sch04] Schaltwerke [Sch04] RALU, Min… [Fer05] Estado-Mac… [Fer05] PIC16F84/… [Fer05] Miscelánea… [Fer05] Femtojava FreeTTS Binary Adder/Subtractor (4 bit)

wikipedia

Para sumar un número de N bits se pueden conectar en paralelo varios circuitos sumadores completos. Para un sumador paralelo de N bits, debe haber N circuitos sumadores completos. Un sumador de arrastre ondulado es un circuito lógico en el que el arrastre de salida de cada sumador completo es el arrastre de entrada del siguiente sumador completo más significativo. Se llama sumador de arrastre por ondulación porque cada bit de arrastre se ondula en la siguiente etapa. En un sumador de acarreo ondulado, la suma y los bits de acarreo de cualquier etapa del sumador medio no son válidos hasta que se produce el acarreo de esa etapa. El retardo de propagación es el tiempo transcurrido entre la aplicación de una entrada y la aparición de la salida correspondiente. Considere una puerta NOT, cuando la entrada es «0» la salida será «1» y viceversa. El tiempo que tarda la salida de la puerta NOT en convertirse en «0» tras la aplicación de un «1» lógico a la entrada de la puerta NOT es el retardo de propagación. Del mismo modo, el retardo de propagación del acarreo es el tiempo transcurrido entre la aplicación de la señal de entrada de acarreo y la aparición de la señal de salida de acarreo (Cout). A continuación se muestra el diagrama del circuito de un sumador de acarreo de 4 bits.